## McCMOS Based Low Power and High Speed 32 x 32 Bit Nikhilum Multiplier

Sarita Chauhan

Assistant Professor, ECE, MLVTEC, Bhilwara, sarita.mlvtec@yahoo.co.in

#### Abstract

Leakage power is the significant component of total power dissipation in nano-scale devices. Leakage power is inversely proportional of channel length. So as the device dimensions are reduced, to incorporate more no of devices, for more function to be performed, subthreshold leakage current & hence leakage power will increases. To reduce the leakage power, channel length has to be increased. So we use non-minimum length transistors to reduce the leakage current thus power. This technique is called Multiple Channel CMOS (McCMOS). Vedic mathematics is the branch of mathematics which depends upon 16 sutra and 13 up-sutra, given between 1911 and 1918 by Sri Bharati Krisna Tirthaji (1884-1960). In this paper we had used McCMOS technique as well as ancient Vedic technique Nikhilum Sutra to reduce the power dissipation and increase the speed of the multiplier. The designed  $32 \times 32$  bit multiplier dissipates a power of 0.556 mW and a propagation delay of 27.82 nsec. 60510 transistors were used in this design. These results are improvements over power dissipations and delays reported in literature for Vedic and Booth Multiplier.

**Keywords:** McCMOS, Vedic Mathematics, CMOS, Leakage current, Urdhva Tiryakbhyam, Nikhilum Sutra, Leakage Power consumption.

## **1.** Introduction:

In order to increase the functionality of any IC, more no of devices are embedded on the same chip. For this individual transistor has to be occupied less area. Hence their dimension has to be decreased. But at same time, Leakage current and leakage power will increases, as these are inversely proportional to the channel length. So there is a compromise. If we want to increase the functionality of the chip we need to embed more no of devices. To embed more no of devices in the same area of chip, we need to scale down the dimension of individual devices. But for nano scale devices, second order effects like DIBL are more pronounced. Hence subthreshold current and power will be more in these devices. To reduce the power we have to increase the channel length. So we use NMOS as increased channel length to control the subthreshold current. Pmos are made with smaller channel length devices. In Vedic mathematics, Nikhilum Sutra, is the method to produce the calculation in less time. Let us discuss these two methods in details.

#### **1.1** McCMOS Technique

We designed a McCMOS inverter and other basic building block. In this all NMOS are made with a channel length of 29 nm and all PMOS are made with 16.5 nm. These data are taken by repeatedly choosing different length and measuring power delay product. The channel length of the PMOSs are taken 0.5 nm higher than the 16nm technology to incorporate the lateral diffusion. The effect of channel length on threshold voltage (and leakage) is very well documented

demonstrating that VTH decreases rapidly as effective channel length (LEFF) is reduced [10].

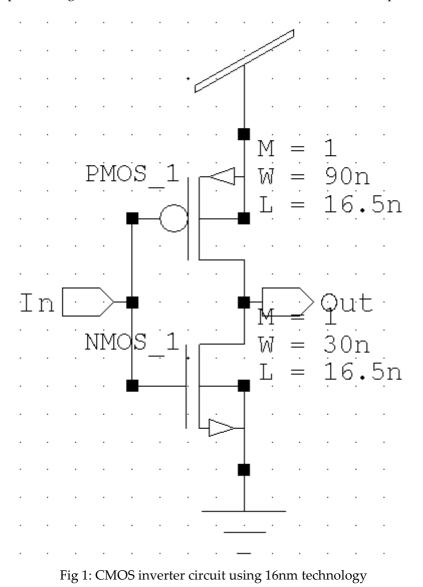

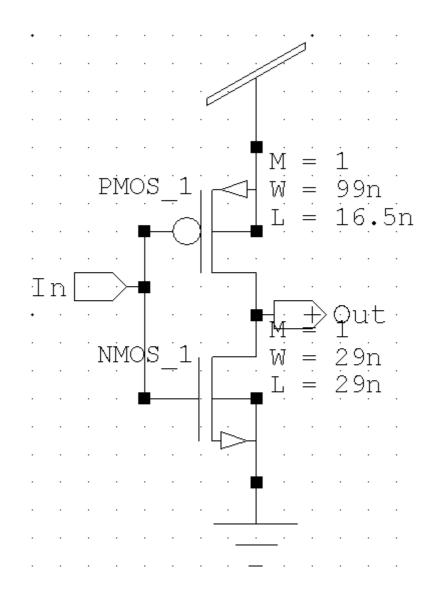

First we optimize the basic gates using McCMOS technique. Fig 1 shows the design of inverter using CMOS, whereas fig 2 shows the inverter circuit using McCMOS technique. Table 1 shows power delay product difference in CMOS inverter and McCMOS inverter. Table 2 shows how we arrive to the specific length & width of the transistor used in McCMOS technique.

From table 1.1 & 1.2 it is clear that McCMOS inverter design with NMOS W=29n L=29n PMOS W=99n L=16.5n is best as far as PDP is concern.

Table 1.1: Comparison of power delay product of CMOS & McCMOS inverter

| Technique | W & L                                    | Power (nW) | Delay<br>(nsec) | PDP ( nW-nsec) |

|-----------|------------------------------------------|------------|-----------------|----------------|

| CMOS      | NMOS W=30n L=16.5n<br>PMOS W=90n L=16.5n | 45.4       | 0.294           | 13.3           |

| McCMOS    | NMOS W=29n L=29n<br>PMOS W=99n L=16.5n   | 42.4       | 0.286           | 12.1           |

Fig 2: McCMOS inverter circuit using 16nm technology

|                  |            | Power   | Delay (n | PDP ( nW- |

|------------------|------------|---------|----------|-----------|

| W & L            |            | (nWatt) | sec)     | nsec)     |

| NMOS W=25n L=25n | PMOS W=25n | 20.05   | 0.47(0   | 10 5070   |

| L=16.5n          |            | 39.05   | 0.4760   | 18.5878   |

| NMOS W=25n L=25n | PMOS W=35n | 40.26   | 0.4060   | 16 2456   |

| L=16.5n          |            | 40.26   | 0.4060   | 16.3456   |

| NMOS W=25n L=25n | PMOS W=50n | 41.10   | 0.3510   | 14.4261   |

| L=16.5n          |            | 41.10   | 0.5510   | 14.4201   |

| NMOS W=25n L=25n | PMOS W=80n | 42.23   | 0.3040   | 12.8379   |

| L=16.5n          |            | 42.23   | 0.3040   | 12.0379   |

| NMOS W=33n L=33n | PMOS W=80n | 42.27   | 0.3040   | 12.8501   |

| L=16.5n          |            | 42.27   | 0.3040   | 12.0301   |

| NMOS W=20n L=20n | PMOS W=80n | 43.23   | 0.3030   | 13.0987   |

| L=16.5n          |            | 40.20   | 0.5050   | 15.0707   |

| NMOS W=40n L=40n | PMOS W=80n | 42.74   | 0.3050   | 13.0357   |

| L=16.5n          |            | 12.71   | 0.5050   | 15.0557   |

| NMOS W=22n L=22n | PMOS W=80n | 42.91   | 0.3030   | 13.0017   |

| L=16.5n          |            | 42.91   | 0.0000   | 10.0017   |

| NMOS W=28n L=28n | PMOS W=80n | 41.92   | 0.3040   | 12.7437   |

| L=16.5n          |            | 11.72   | 0.0040   | 12.7 107  |

| NMOS W=30n L=30n | PMOS W=80n | 41.94   | 0.3040   | 12.7498   |

| L=16.5n          |            | 11.71   | 0.0040   | 12.7 490  |

| NMOS W=29n L=29n | PMOS W=80n | 41.90   | 0.3040   | 12.7376   |

| L=16.5n          |            | 11.90   | 0.0010   | 12.7070   |

| NMOS W=27n L=27n | PMOS W=80n | 41.98   | 0.3040   | 12.7619   |

| L=16.5n          |            | 11.90   | 0.0010   | 12.7 017  |

| NMOS W=28n L=28n | PMOS W=99n | 42.38   | 0.2860   | 12.1207   |

| L=16.5n          |            | 12.00   | 0.2000   | 12.1207   |

| NMOS W=29n L=29n | PMOS W=99n | 42.36   | 0.2860   | 12.1150   |

| L=16.5n          |            | 12.00   | 0.2000   | 12.1100   |

## Table 1.2: Comparison of PDP in McCMOS inverter using different lengths & Widths

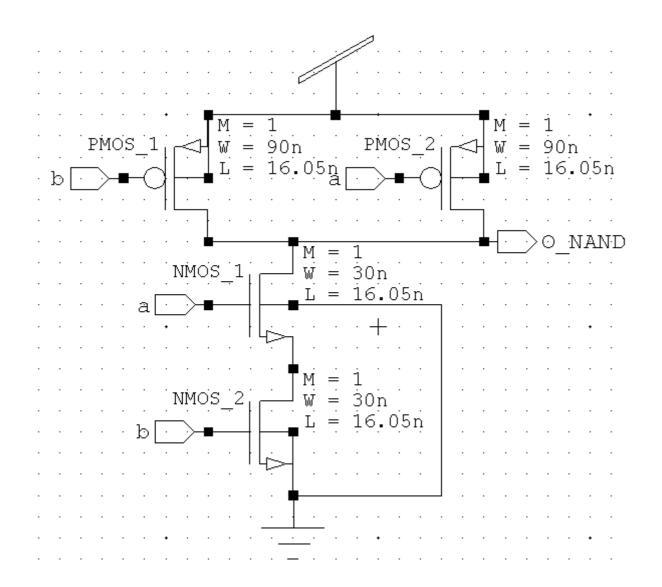

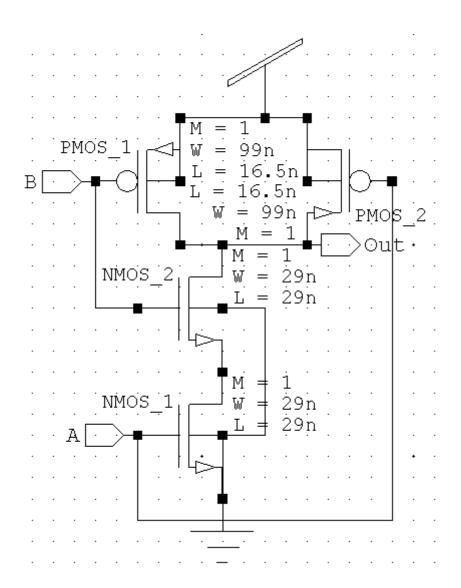

Fig 3 & 4 shows the circuit of CMOS and McCMOS based nand circuit.

Fig 3: CMOS 2 input NAND circuit using 16nm technology

Fig 4: McCMOS 2 input NAND circuit using 16nm technology

From the table 1.3 it is clear that in McCMOS based nand circuit power & delay are much improved in comparison to its counterpart of CMOS nand circuit.

Similarly other basic component are simulated using McCMOS and CMOS and it has been verified that McCMOS based circuit has less power as well as less delay.

Table 1.3: Comparison of power & delay in CMOS & McCMOS based nand circuit.

| Technique |                                         | Power   | Delay   | PDP       |

|-----------|-----------------------------------------|---------|---------|-----------|

|           | Length & Width                          | (nWatt) | (n Sec) | (atta Ws) |

| CMOS      | NMOS W=30n L=16.05n PMOS W=90n L=16.05n | 92.30   | 0.40    | 37.20     |

| McCMOS    | NMOS W=29n L=29n PMOS W=99n L=16.5n     | 64.08   | 0.34    | 21.53     |

## **2.** Vedic Mathematics

The ancient system of Vedic Mathematics was rediscovered from the Indian Sanskrit texts known as the Vedas, between 1911 and 1918 by Sri Bharati Krisna Tirthaji (1884-1960) from the Atharva Vedas. According to his research all of mathematics is based on sixteen Sutras, or word-formulas [11]. The description of urthatryakbhyam sutra and nighilum suta is given in [

## DESIGN OF THE 32x32 BIT UT MULTIPLIER

# In the design for 32x32 bit UT multiplier using McCMOS technique, we designed fundamental blocks like

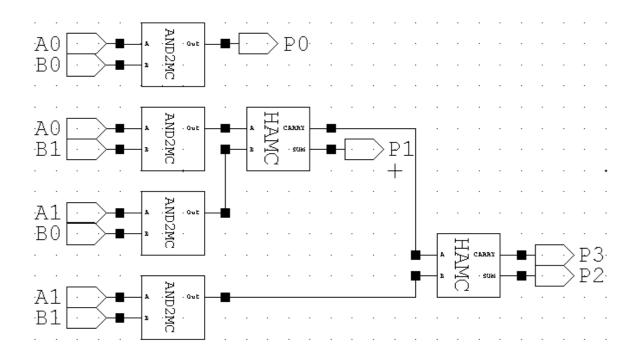

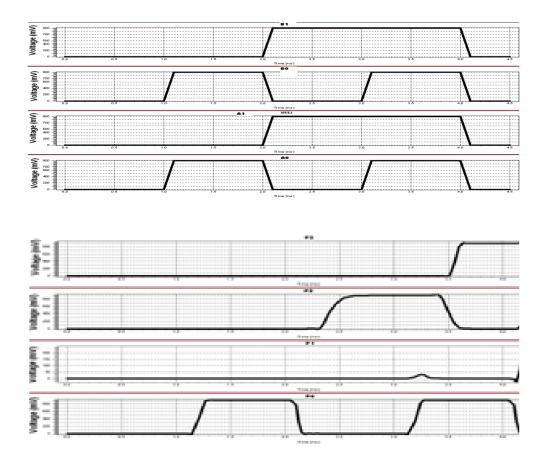

- 2x2 bit UT multiplier using McCMOS technique (fig. 5 shows schematic design & fig. 6 shows waveform)

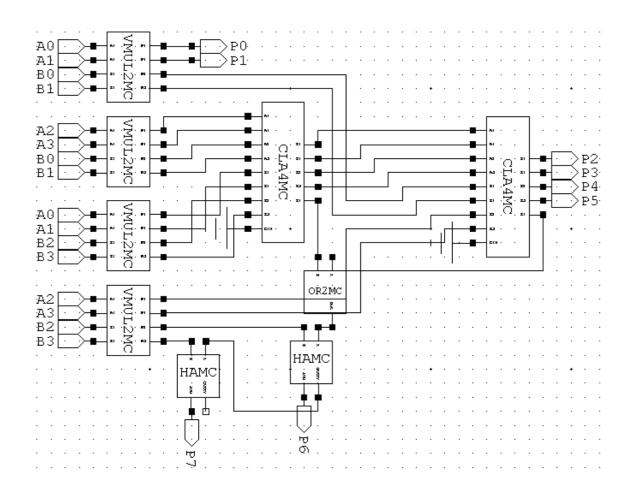

- 4x4 bit UT multiplier using McCMOS technique (fig. 7 shows schematic design)

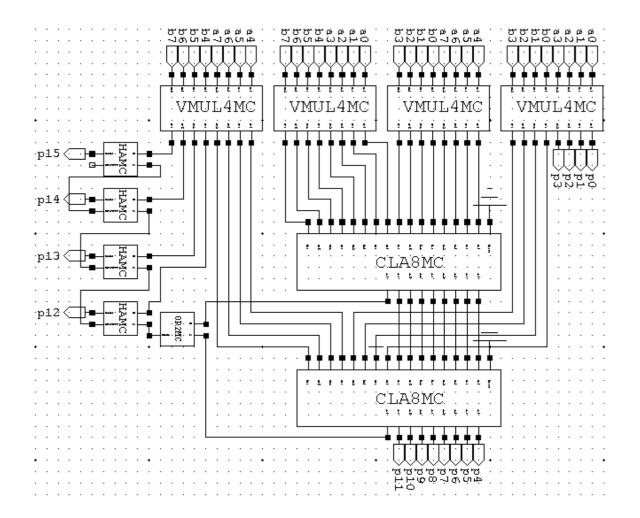

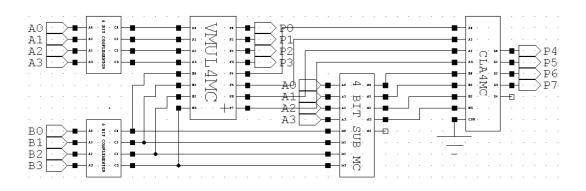

- 8x8 bit UT multiplier using McCMOS technique (fig. 8 shows schematic design)

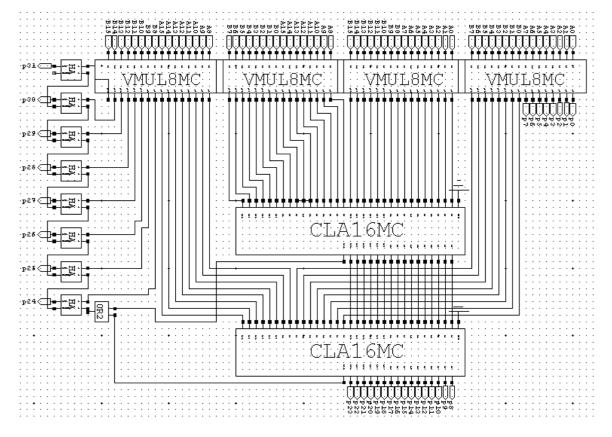

- 16x16 bit UT multiplier using McCMOS technique (fig.9 shows schematic design)

- 32x32 bit UT multiplier using McCMOS technique (fig. 10 shows schematic design)

The comparison of delay, power, no of transistor used in different designed multipliers is illustrated in table 2.1.

| Multiplier   | Delay      | Power     | Power-delay       | No. of transistor |

|--------------|------------|-----------|-------------------|-------------------|

|              |            |           | product           | used              |

| 2x2 CMOS     | 30.12 nsec | 0.7114 μW | 21.0746 nsec- μW  | 60                |

| 4x4 McCMOS   | 29.68 nsec | 4.97 μW   | 21.42737 nsec- μW | 618               |

| 4x4 CMOS     | 30.14 nsec | 4.96 μW   | 147.5096 nsec- μW | 618               |

| 8x8 McCMOS   | 29.67 nsec | 26.31 μW  | 149.4944 nsec- μW | 3222              |

| 8x8 CMOS     | 30.14 nsec | 26.92 μW  | 780.6177 nsec- μW | 3222              |

| 16x16 McCMOS | 29.68 nsec | 0.108 mW  | 811.3688 nsec- mW | 14382             |

| 16x16 CMOS   | 30.14 nsec | 0.130 mW  | 3.20544 nsec- mW  | 14382             |

| 32x32 McCMOS | 29.68 nsec | 0.564 mW  | 3.9182 nsec- mW   | 60510             |

| 32x32 CMOS   | 30.12 nsec | 0.575 mW  | 16.73952 nsec- mW | 60510             |

## Table 2.1 Comparison of Designed UT Multipliers

The comparison of delay, power, no of transistor used in reported work and proposed multiplier is illustrated in table 2.2.

| UT Multiplier            | Delay       | Power    | Power-delay       | No. of transistor |

|--------------------------|-------------|----------|-------------------|-------------------|

|                          |             |          | product           | used              |

| Paper [2]                | 59 nsec     | 500 mW   | 16615.2 nsec- mW  | 23600             |

| Paper [3]                | 15 ns       | 277 mW   | 1179.38 nsec- mW  | 27704             |

| Paper [6] with<br>CSA    | 96.5 ns     | 22.1 mW  | 29.5 nsec- mW     | -                 |

| Paper [6] with<br>CLA    | 54.1 ns     | 21.8 mW  | 2132.65 nsec- mW  | -                 |

| Paper [7]                | 29.67 nsec. | 0.56 mW  | 17.319 nsec- mW   | 60510             |

| Proposed 32x32<br>CMOS   | 30.12 nsec  | 0.575 mW | 16.73952 nsec- mW | 60510             |

| Proposed 32x32<br>McCMOS | 29.68 nsec  | 0.564 mW | 3.9182 nsec- mW   | 60510             |

## Table 2.2 Comparison of UT Multiplier with Reported Work

Our proposed 32x32 bit multiplier using McCMOS and UT Sutra of Vedic mathematics is much far better as compared to reported work in terms of Power-Delay Product.

Figure 5) 2 x 2 Bit Multiplier and & its symbol

Figure 6 Input Output waveforms of 2x2 Bit multiplier

Figure7) 4 x 4 Bit Multiplier

Figure8) 8 x 8 Bit Multiplier

#### Sarita CHauhan MCCMOS BASED LOW POWER AND HIGH SPEED 32 X 32 BIT NIKHILUM MULTIPLIER

Figure10) 32 x 32 Bit Multiplier

## **2.** Design Of The 32x32 Bit Nikhilum Multiplier

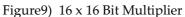

The basic structure of the Nikhilum Multiplier is shown in fig11. In the design for 32x32 bit Nikhilum (NM) Multiplier using McCMOS technique, we designed following fundamental blocks:

- 2x2 bit NM multiplier using McCMOS technique (fig. 12 shows schematic design )

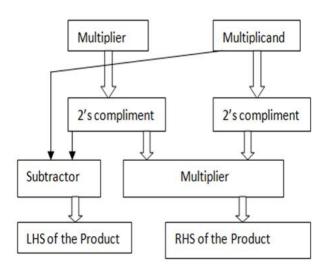

- 4x4 bit NM multiplier using McCMOS technique (fig. 13 shows schematic design)

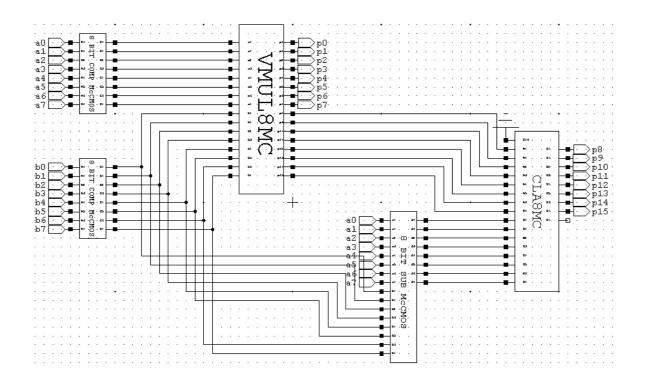

- 8x8 bit NM multiplier using McCMOS technique (fig. 14 shows schematic design)

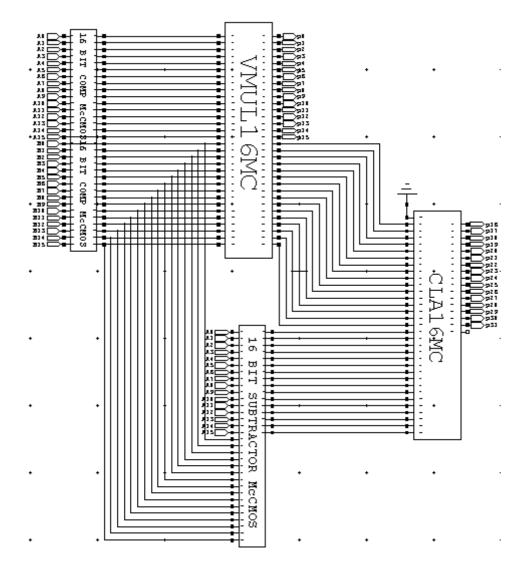

- 16x16 bit NM multiplier using McCMOS technique (fig.15 shows schematic design)

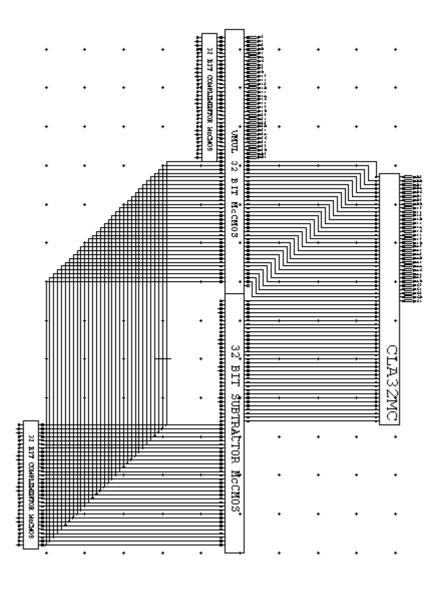

- 32x32 bit NM multiplier using McCMOS technique (fig. 16 shows schematic design)

### STEPS INVOLVED FOR MULTIPLICATION USING NIKHILUM (NM) SUTRA

Fig 11 Block Diagram of Nikhilum Sutra

Figure12) 4 x 4 Bit Multiplier

Figure13) 8 x 8 Bit Multiplier

Figure14) 16 x 16 Bit Multiplier

Figure 15) 32 x 32 Bit Multiplier

## **3.** Conclusion

The proposed Vedic multiplier (discussed in section 3) is simulated using Tanner Tool v14.1. The Comparison between proposed multiplier and other reported multiplier is shown in table I.

DOMED

| POWER  |          |          |          |          |  |  |

|--------|----------|----------|----------|----------|--|--|

|        | UT       | UTMcCMOS | NM       | NMMcCMOS |  |  |

| 4-BIT  | 4.96E-06 | 4.98E-06 | 8.39E-06 | 4.78E-06 |  |  |

| 8-BIT  | 2.69E-05 | 2.63E-05 | 1.94E-05 | 1.87E-05 |  |  |

| 16-BIT | 1.30E-04 | 1.09E-04 | 1.20E-04 | 1.17E-04 |  |  |

| 32-BIT | 5.75E-04 | 5.64E-04 | 5.60E-04 | 5.56E-04 |  |  |

## Table 4.1: Comparison of Vedic multiplier

| D | EI | A | Y |  |

|---|----|---|---|--|

|   |    |   |   |  |

#### Sarita CHauhan MCCMOS BASED LOW POWER AND HIGH SPEED 32 X 32 BIT NIKHILUM MULTIPLIER

|        | UT       | UTMcCMOS | NM       | NMMcCMOS |

|--------|----------|----------|----------|----------|

| 4-BIT  | 3.01E-08 | 2.97E-08 | 2.90E-08 | 2.84E-08 |

| 8-BIT  | 3.01E-08 | 2.97E-08 | 2.89E-08 | 2.83E-08 |

| 16-BIT | 3.01E-08 | 2.97E-08 | 2.88E-08 | 2.81E-08 |

| 32-BIT | 3.01E-08 | 2.97E-08 | 2.78E-08 | 2.78E-08 |

#### Table 4.2: Comparison of 32x32 bit multipliers

| S. No. | Parameter of                     | Paper | Paper | Paper     | Paper   | Nikhilum |

|--------|----------------------------------|-------|-------|-----------|---------|----------|

|        | comparison                       | [2]   | [3]   | [5]       | [6]     | Design   |

| 1      | Delay (ns)                       | 59    | 15    | 625.292   | 54.1    | 27.82    |

| 2      | Power (mW)                       | 500   | 277   | 29.34     | 21.8    | 0.556    |

| 3      | Power-Delay Product<br>(mW-nsec) | 29500 | 4155  | 18346.067 | 1179.38 | 15.46792 |

| 4      | Transistors<br>used              | 23600 | 27704 | -         | -       | 64862    |

As shown in the table 4.2 our designed is much better in terms of Power dissipation. Also delay is improved. No of transistor is large but this is the sacrifice we have to pay for a less power delay product. The **99% improvement in PDP with respect to the lowest paper [6] is achieved.**

## 4. Acknowledgement:

We sincerely thanks to the PTM website to provide the Technology file of 16 nm.

## References

- [1] YOSHIHISA HARATA, et al., "A High-Speed Multiplier Using a Redundant Binary Adder Tree", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. SC-22,NO. 1, FEBRUARY1987

- [2] SHOJI KAWAHITO,et. al., "A 32 X 32-bit Multiplier Using Multiple-Valued MOS Current-Mode Circuits", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 23, NO. 1, FEBRUARY 1988

- [3] MASATO NAGAMATSU, "A 15-ns 32 X 32-b CMOS Multiplier with an Improved Parallel Structure", IEEE JOURNAL OF SOLID-STATECIRCUITS, VOL. 25, NO. 2, APRIL 1990

- [4] Hanho LEE, "Power Aware Scalable Pipelined Booth Multiplier" IEICE Transaction on faudamentals, Vol. E-88-A, NO. 11, Nov. 2005.

- [5] Hasan Krad and Aws Yousif Al-Taie, "Performance Analysis of a 32-Bit Multiplier with a Carry-Look-Ahead Adder and a 32-bit Multiplier with a Ripple Adder using VHDL", Journal of Computer Science 4 (4): 305-308, 2008 ISSN 1549-3636© 2008 Science Publications

- [6] Raminder Preet Pal Sing1, Parveen Kumar, Balwinder Singh, "Performance Analysis of 32-Bit Array Multiplier with a Carry Save Adder and with a Carry-Look-Ahead Adder", International Journal of Recent Trends in Engineering, Vol 2, No. 6, November 2009.

- [7] D.Venu Gopal1\* and M. Mohan Reddy, "Design and Implementation of a Fast Unsigned 32bit Multiplier Using Verilog HDL", International Journal of Computer Sciences and Engineering, Volume-2, Issue-5 E-ISSN: 2347-2693, 2014.

- [8] Sumit Vaidya and Deepak Dandekar. "delay-power performance comparison of multipliers in vlsi circuit design". International Journal of Computer Networks & Communications (IJCNC), Vol.2, No.4, July 2010

- [9] Dr. K.S. Gurumurthy, M.S Prahalad "Fast and Power Efficient 16×16 Array of Array Multiplier using Vedic Multiplication",

- [10] M. Ramalatha, K. Deena Dayalan, P. Dharani, S. Deborah Priya," High Speed Energy Efficient ALU Design using Vedic Multiplication Techniques ", ACTEA 2009

- [11] Abhijit Asati and Chandrashekhar "A High-Speed, Hierarchical 16×16 Array of Array Multiplier Design", IMPACT 2009.

- [12] Kevin Biswas, "Multiplexer Based Array Multipliers," A Ph.D. Dissertation, University of Windsor, Electrical and Computer Engineering, Apr. 2005.

- [13] Himanshu Thapliyal and Hamid R. Arabnia, "A time area power efficient multiplier and square architecture based on ancient Indian Vedic mathematics,www.vedicmathsindia.org.

- [14] Vishal Verma and Himanshu Thapliyal, "High Speed Efficient N X N Bit Multiplier Based On Ancient Indian Vedic Mathematics", Proceedings International Conference On VLSI, Las Vegas, June 2003.